6. Sekvensnät

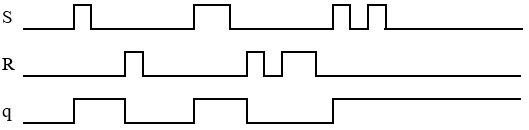

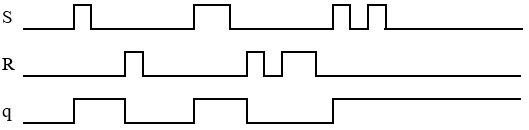

6.1.1

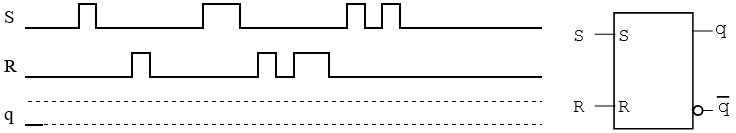

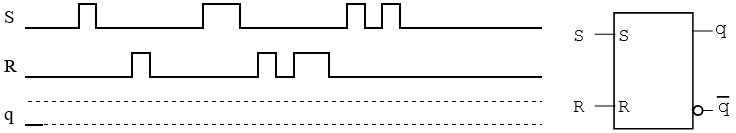

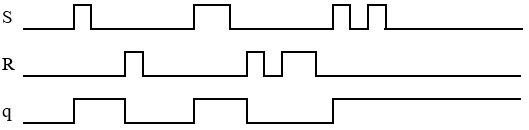

I figuren visas en SR-latch jämte tidsdiagram för S-, och R- signalerna.

Komplettera tidsdiagrammet med q, då q =0 från början.

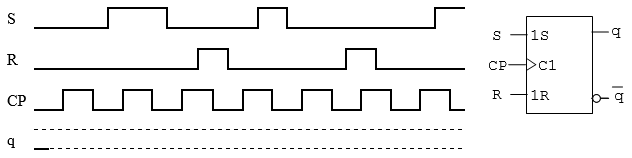

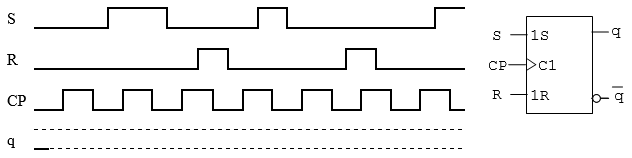

6.1.2

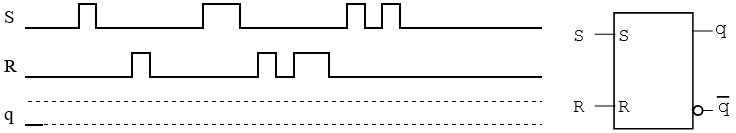

I figuren visas en SR-vippa jämte tidsdiagram för S-, R- och CP-signalerna.

Komplettera tidsdiagrammet med q, då q =0 från början.

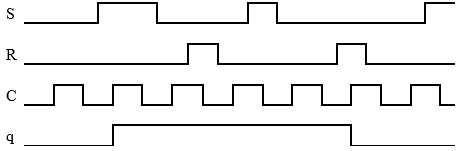

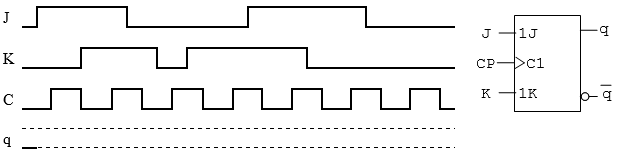

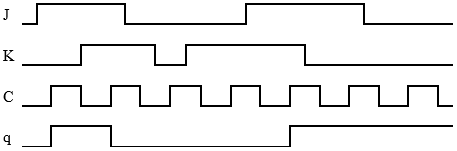

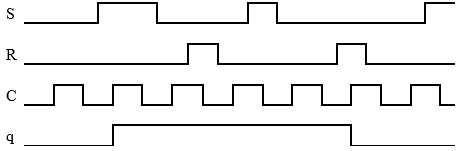

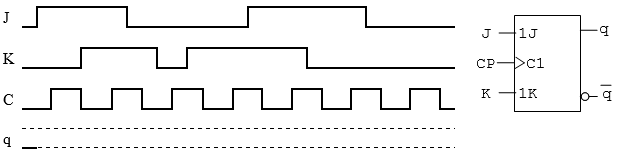

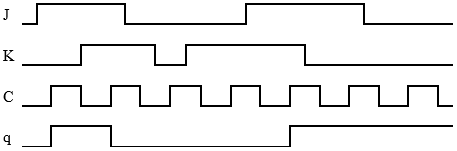

6.1.3

I figuren visas en flanktriggad JK-vippa jämte tidsdiagram för J-, K- och CP-signalerna.

Komplettera tidsdiagrammet med q, då q =0 från början.

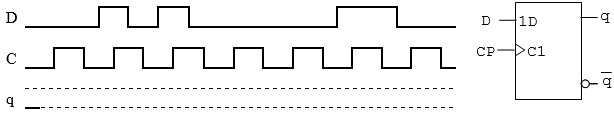

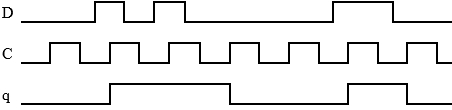

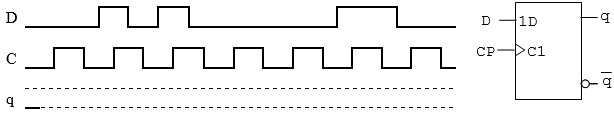

6.1.4

I figuren visas en D-vippa jämte tidsdiagram för D- och CP-signalerna.

Komplettera tidsdiagrammet med q, då q =0 från början.

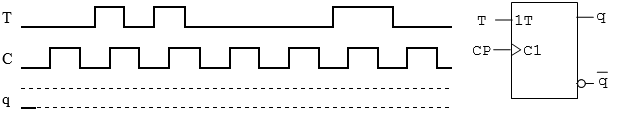

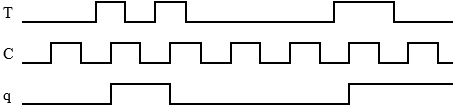

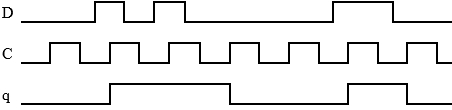

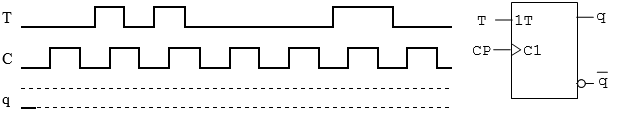

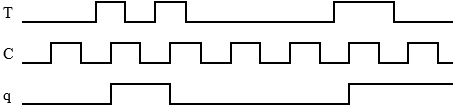

6.1.5

I figuren visas en T-vippa jämte tidsdiagram för T- och CP-signalerna.

Komplettera tidsdiagrammet med q, då q =0 från början.

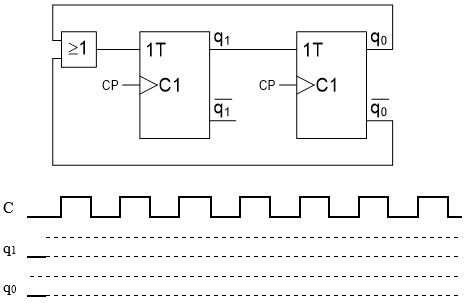

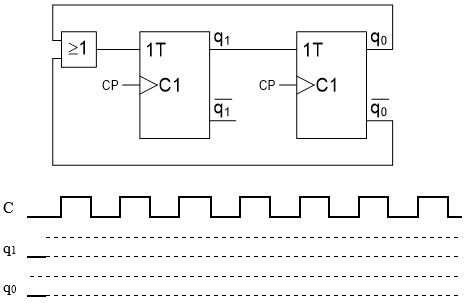

6.2.1

Rita tillståndsgraf och färdigställ tidsdiagrammet för den autonoma räknaren.

Tidsdiagrammet skall utgå från tillståndet Q = (q

1q

0) = 0.

(Börja med att ställa upp tillståndstabellen).

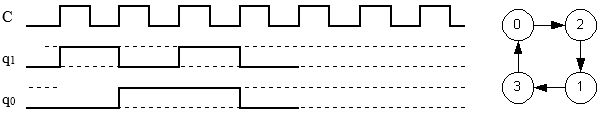

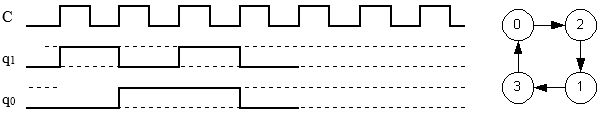

6.2.2

Rita tillståndsgraf och tidsdiagram för den autonoma räknaren.

Tidsdiagrammet skall utgå från tillståndet Q = (q

2q

1q

0) = 0.

(Börja med att ställa upp tillståndstabellen).

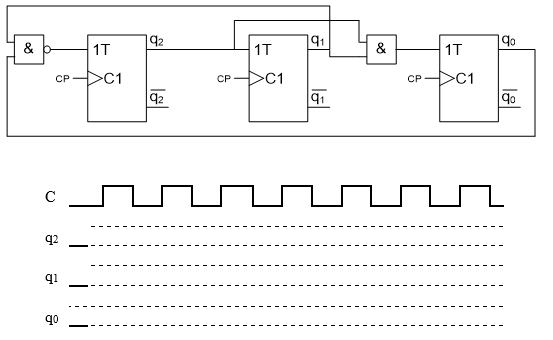

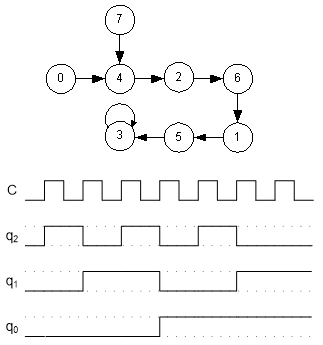

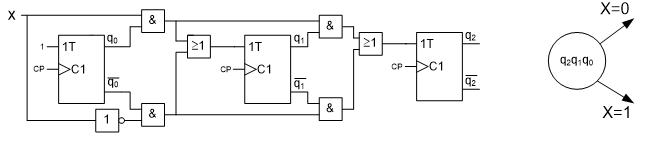

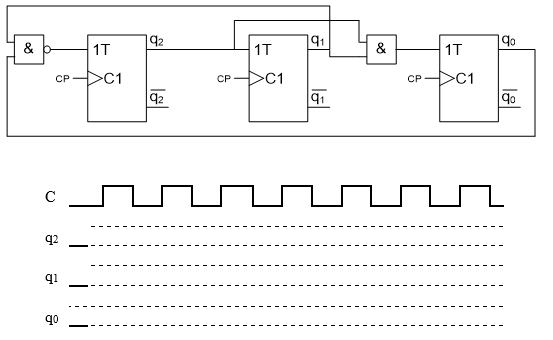

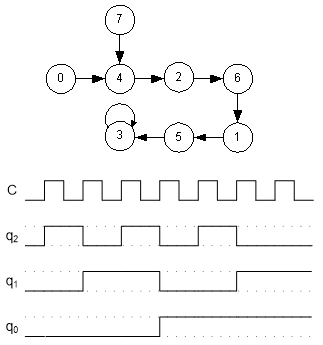

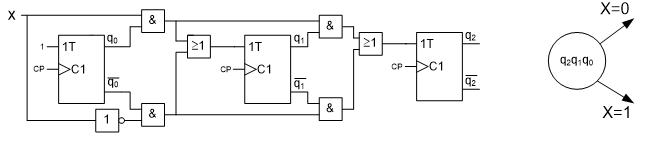

6.2.3

Analysera räknaren nedan. Utgå från initialtillståndet 0,

vilken räknesekvens motsvarar räknarens tillståndsgraf?

Tillstånden kodas som binärt tal: q

2 q

1 q

0.

a) 0,1,2,3,4,5,6,7,0...

b) 0,2,4,6,7,1,3,5,0...

c) 0,2,4,7,6,1,3,5,0...

alternativ b.

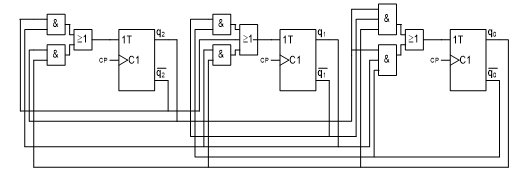

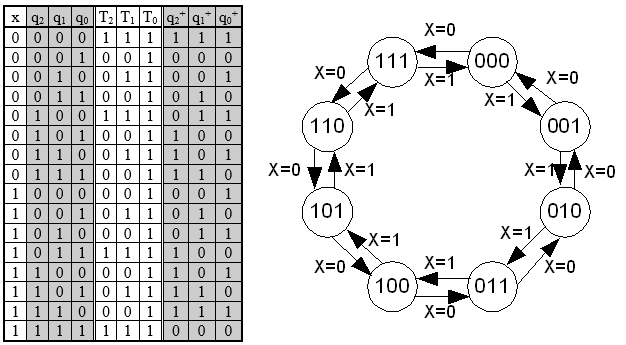

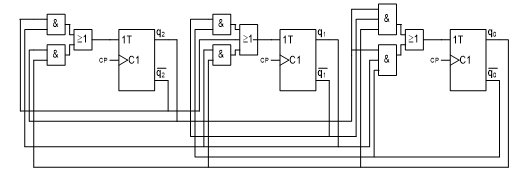

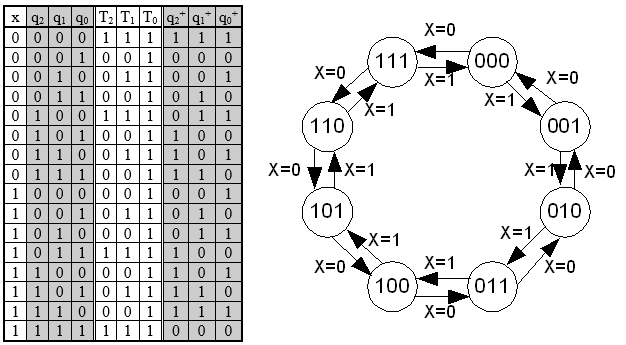

6.2.4

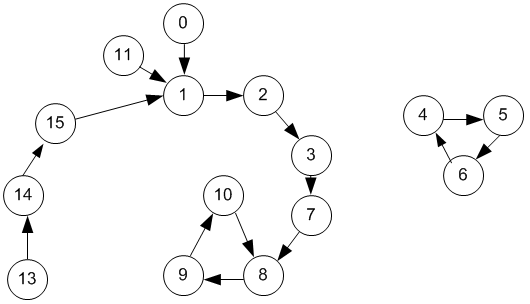

Analysera räknaren nedan. Visa dess fullständiga tillståndsgraf.

Tillstånden kodas som binärt tal: q

2 q

1 q

0.

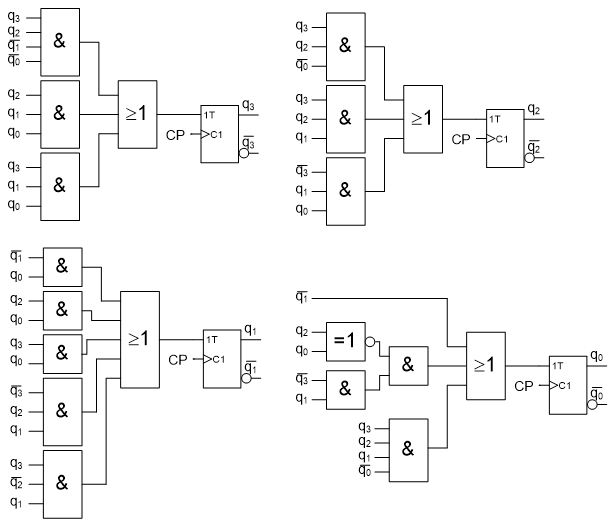

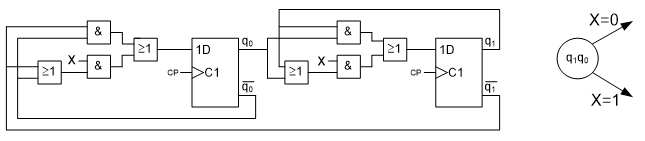

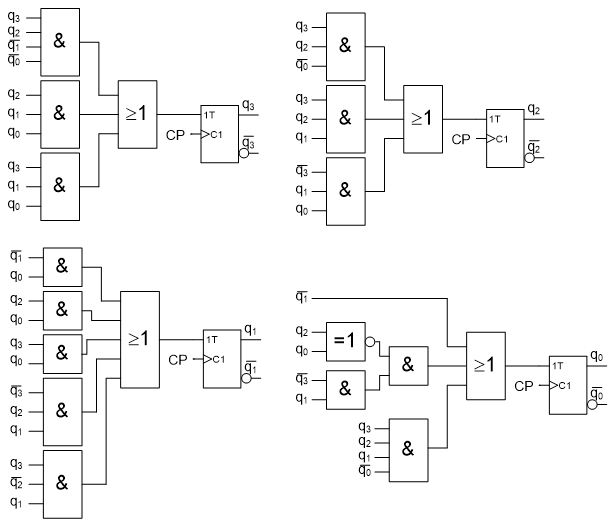

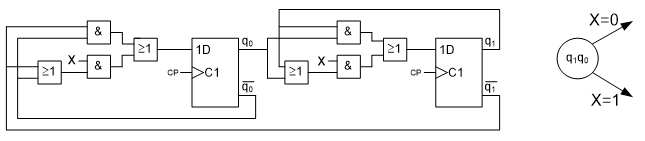

6.3.1

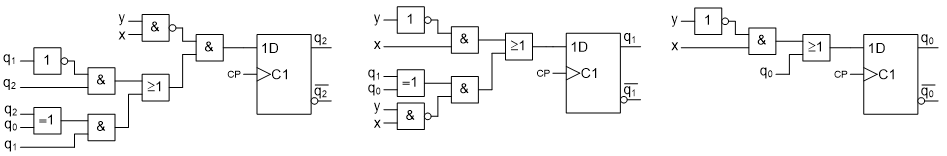

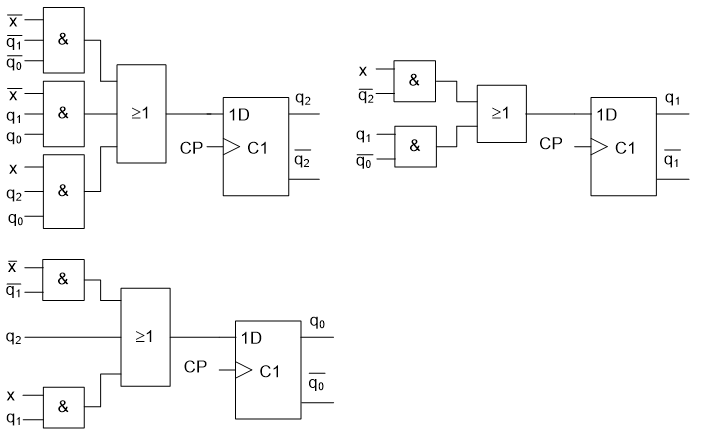

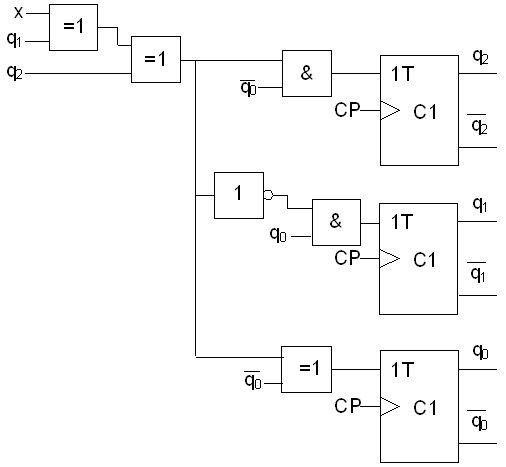

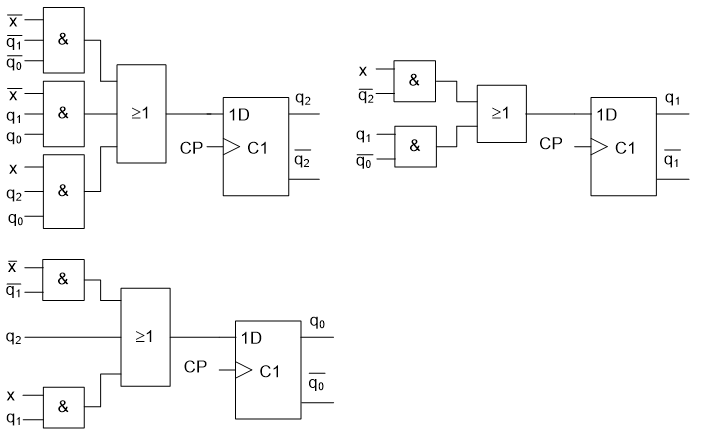

Ställ upp funktionstabell och rita tillståndsgrafen för följande räknare med räknevillkoret x.

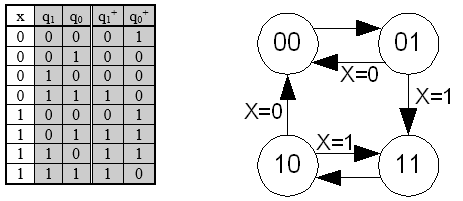

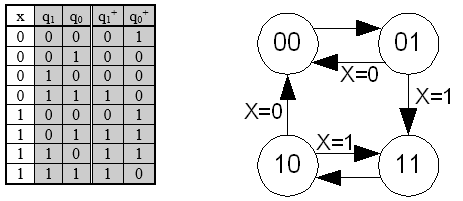

6.3.2

Ställ upp funktionstabell och rita tillståndsgrafen för följande räknare med räknevillkoret x.

6.4.1 Konstruera en autonom synkron modulo-6 räknare med räknesekvens:

q

2 q

1 q

0 = 000, 001, 101, 111, 011, 010, 000 och vipptyp enligt nedan.

a) med D-vippor, och där AND-, OR- och INVERTERAR-grindar också får användas.

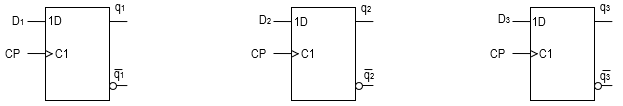

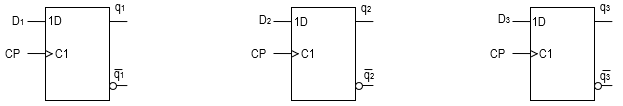

Vi ska alltså bestämma funktionerna D

1, D

2 och D

3 i följande nät:

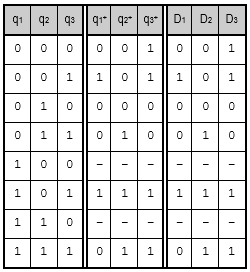

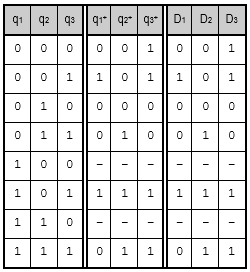

För D-vippor gäller att nästa tillstånd (q+) är lika med D-värdet före klockningen.

Därför skall D-värdet för varje D-vippa väljas till motsvarande q+ -värde i tillståndstabellen.

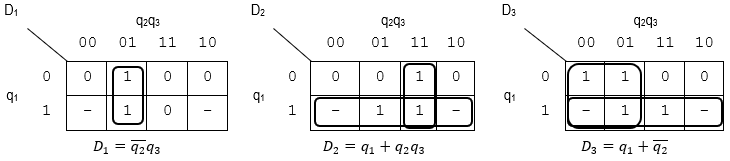

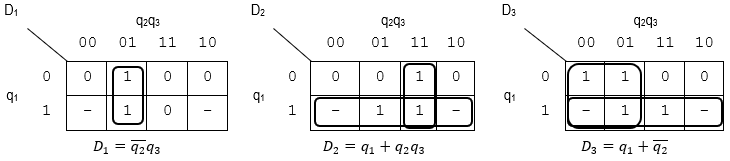

Minimering av funktionerna för D

1, D

2 och D

3

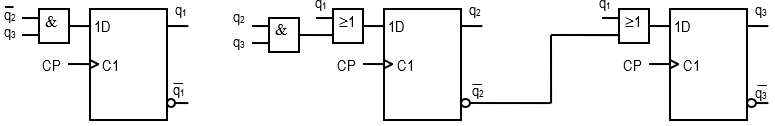

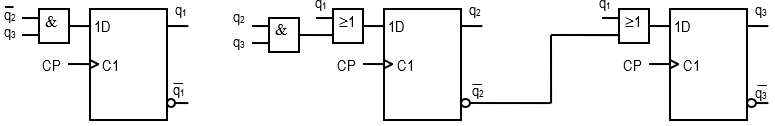

Slutligen, realisering med D-vippor

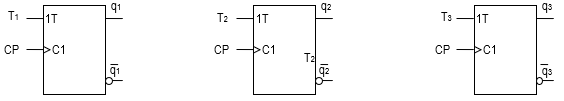

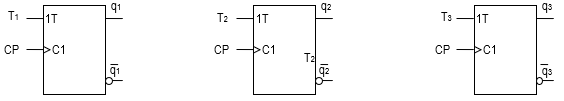

b) med T-vippor, och där AND-, OR- och INVERTERAR-grindar också får användas.

Vi ska alltså bestämma funktionerna T

1, T

2 och T

3 i följande nät:

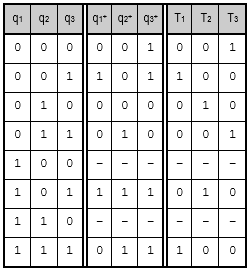

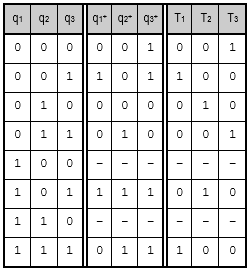

T-vippans funktion läggs till tillståndstabellen:

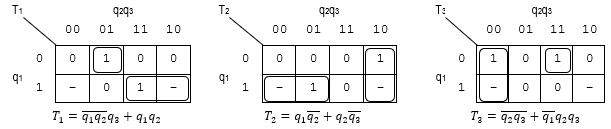

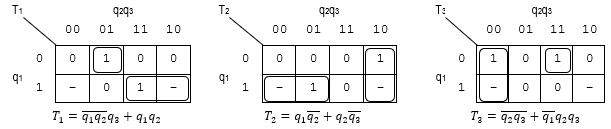

Minimering av funktionerna för T

1, T

2 och T

3

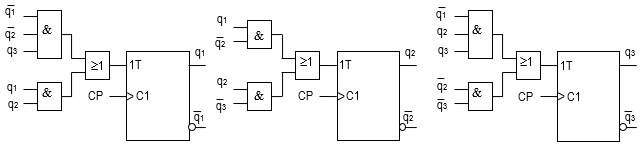

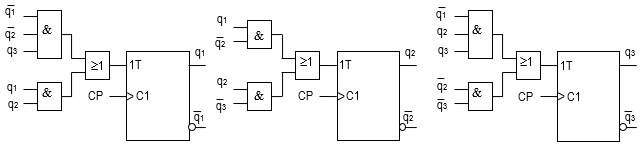

Realisering med T-vippor

6.5.1 Konstruera en synkron räknare med en styrsignal x,

som bestämmer räknarens funktion på följande sätt:

x = 0 Räknaren räknar enligt sekvensen q

1q

0 = 00, 01, 11, 10, 00

x = 1 Räknaren räknar enligt sekvensen q

1q

0 = 00, 10, 11, 01, 00

Av de två sekvenserna ovan framgår att räknaren är reversibel dvs. den kan räkna en bestämd sekvens framåt eller bakåt.

Använd T-vippor och valfria grindar.

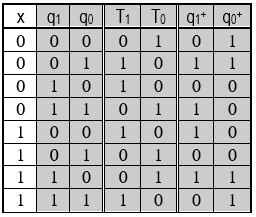

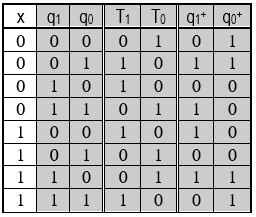

Tillståndstabellen blir:

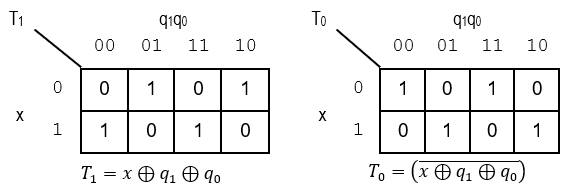

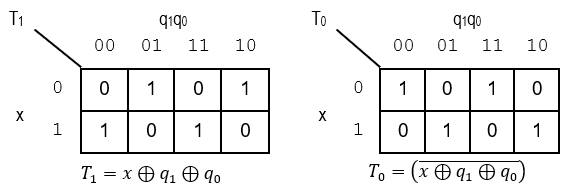

Minimering av T-funktionerna:

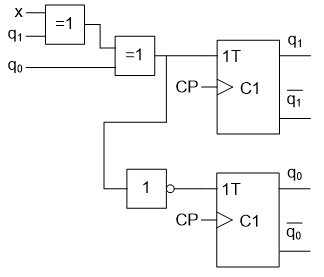

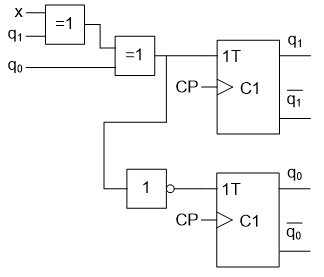

Realisering:

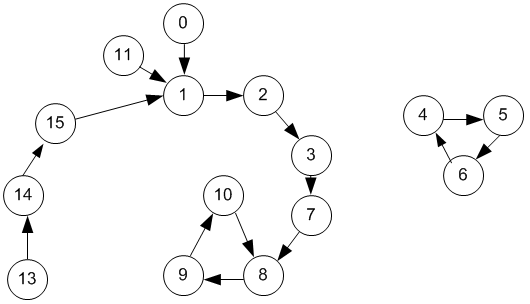

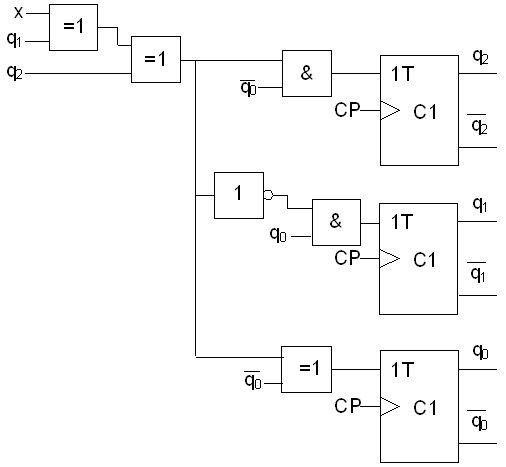

6.5.2

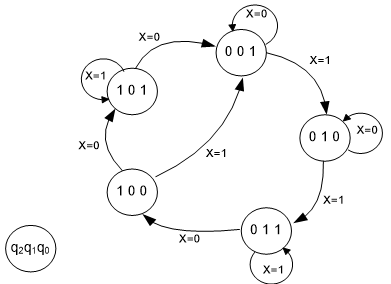

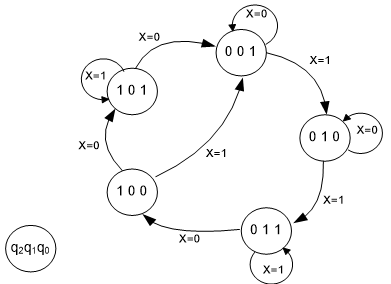

Konstruera en räknare med styrsignal x, som realiserar följande tillståndsgraf.

Använd D-vippor, och grindarna AND, OR och INVERTERARE.

Förutsätt att räknaren alltid startar i tillstånd 001.

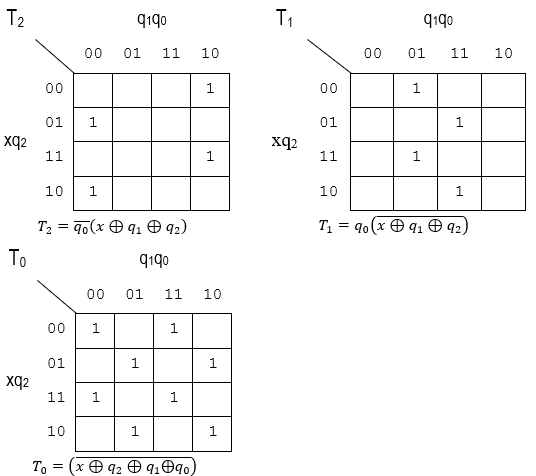

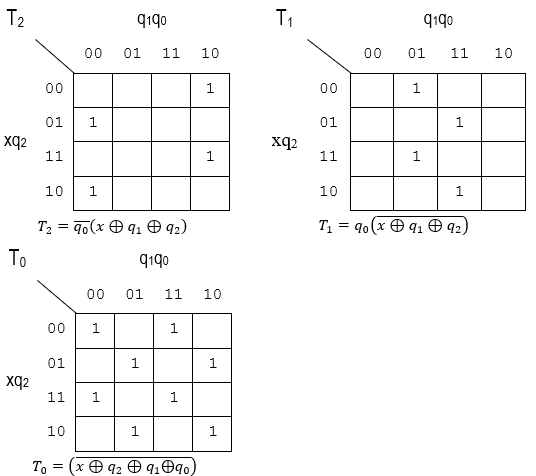

6.5.3 Konstruera en synkron, reversibel räknare med en styrsignal x, vilken bestämmer räknarens funktion enligt:

x = 0: Sekvensen 000,001,011,010,110,111,101,100,000 (Gray-kod)

x = 1: Sekvensen 000,100,101,111,110,010,011,001,000 (Gray-kod baklänges)

T-vippor och valfria grindar får användas.

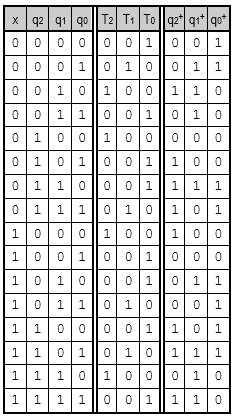

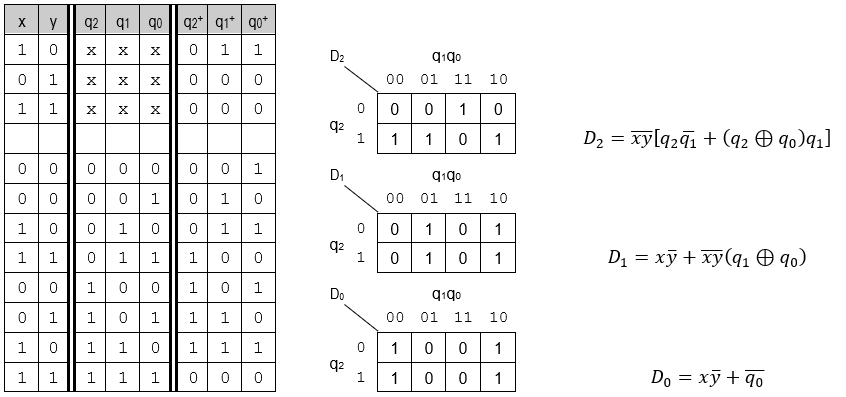

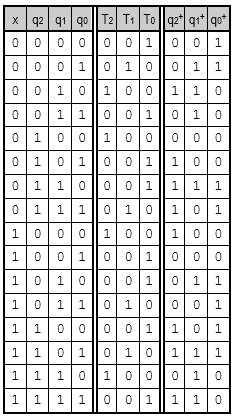

Tillståndstabellen blir:

Minimering av T-funktionerna:

Realisering:

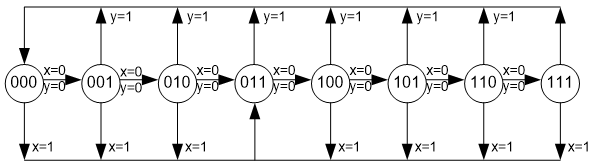

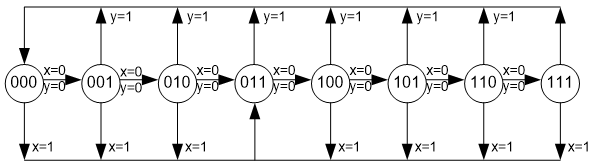

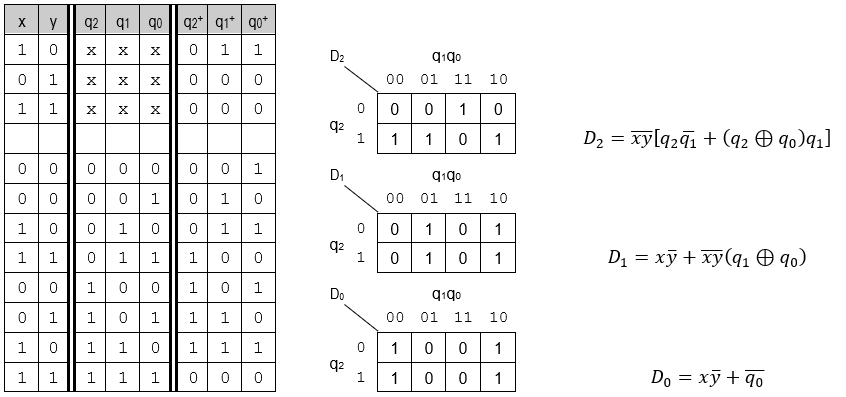

6.6.1 5.17 Konstruera en synkron räknare med styrsignaler x och y som bestämmer räknarens funktion på följande sätt:

y = 1: Räknaren försätts i tillstånd 000.

y = 0:

x = 0: Räknaren räknar enligt sekvensen q

2 q

1q

0 = 000,001,010,011,100,101,110,111,000...

x = 1: Räknaren försätts i tillstånd 011.

D-vippor och valfria grindar får användas. Rita också en tillståndsgraf som beskriver räknaren.

Räknarens tillståndsgraf:

Tittståndsdiagram och minimering:

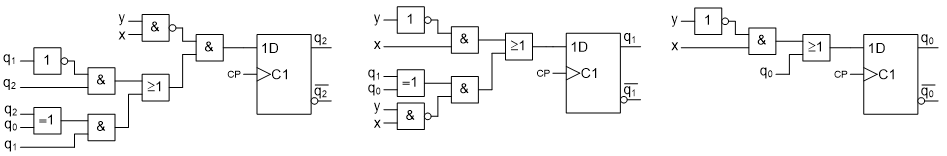

Realisering:

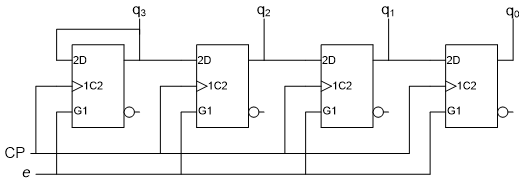

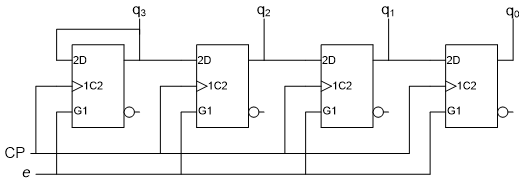

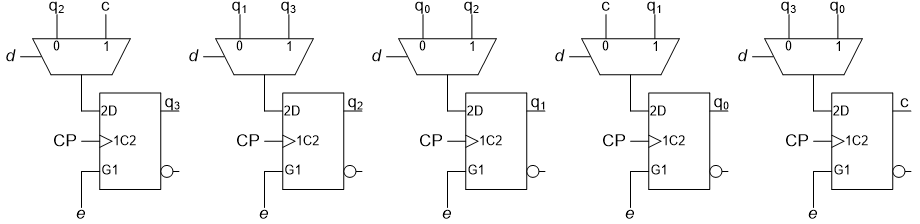

6.6.2 Konstruera ett 4-bitars synkront skiftregister (q

3q

2q

1q

0) med D-vippor och valfria komponenter för den kombinatoriska delen. Kretsen ska ha en styrsignal

e (enable):

e = 0: skiftregister kvarstannar i befintligt tillstånd

e = 1: ett aritmetiskt högerskift utförs.

Utskiftad bit q

0 ignoreras.

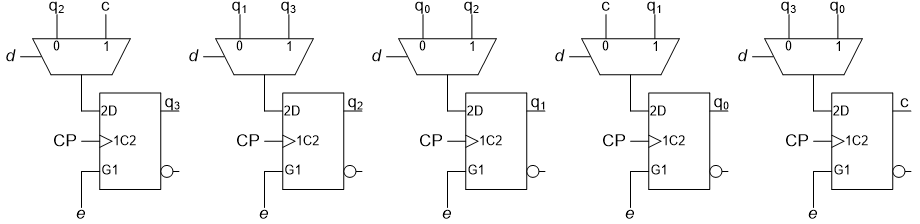

6.6.3 Konstruera ett 4-bitars synkront skiftregister (q

3q

2q

1q

0) med D-vippor och valfria kombinatoriska komponenter. Kretsen ska ha två styrsignaler

e (enable) och

d (direction):

e = 0: skiftregister kvarstannar i befintligt tillstånd

e = 1: ett skift utförs.

d = 0: “vänsterskift”

d = 1: “högerskift”

Utskiftade bitar (q

3 vid vänsterskift och q

0 vid högerskift) placeras i en D-vippa med beteckningen

c. Inskiftade bitar (q

0 vid vänsterskift och q

3 vid högerskift) tas från D-vippa

c.

a) 0,1,2,3,4,5,6,7,0...

b) 0,2,4,6,7,1,3,5,0...

c) 0,2,4,7,6,1,3,5,0...

alternativ b.

a) 0,1,2,3,4,5,6,7,0...

b) 0,2,4,6,7,1,3,5,0...

c) 0,2,4,7,6,1,3,5,0...

alternativ b.

För D-vippor gäller att nästa tillstånd (q+) är lika med D-värdet före klockningen.

Därför skall D-värdet för varje D-vippa väljas till motsvarande q+ -värde i tillståndstabellen.

För D-vippor gäller att nästa tillstånd (q+) är lika med D-värdet före klockningen.

Därför skall D-värdet för varje D-vippa väljas till motsvarande q+ -värde i tillståndstabellen.

Minimering av funktionerna för D1, D2 och D3

Minimering av funktionerna för D1, D2 och D3

Slutligen, realisering med D-vippor

Slutligen, realisering med D-vippor

b) med T-vippor, och där AND-, OR- och INVERTERAR-grindar också får användas.

Vi ska alltså bestämma funktionerna T1, T2 och T3 i följande nät:

b) med T-vippor, och där AND-, OR- och INVERTERAR-grindar också får användas.

Vi ska alltså bestämma funktionerna T1, T2 och T3 i följande nät:

T-vippans funktion läggs till tillståndstabellen:

T-vippans funktion läggs till tillståndstabellen:

Minimering av funktionerna för T1, T2 och T3

Minimering av funktionerna för T1, T2 och T3

Realisering med T-vippor

Realisering med T-vippor

Minimering av T-funktionerna:

Minimering av T-funktionerna:

Realisering:

Realisering:

Minimering av T-funktionerna:

Minimering av T-funktionerna:

Realisering:

Realisering:

Tittståndsdiagram och minimering:

Tittståndsdiagram och minimering:

Realisering:

Realisering: